1 引言

軟件無線電是一種基于高速、高精度A/D轉換器與高速FPGA/DSP器件,并以軟件為核心的嶄新體系結構。受A/D轉換器制約,直接采樣處理射頻信號有一定難度,因此目前普遍采用中頻數字化方案:射頻信號首先進入接收天線,然后送入射頻前端處理。這種結構與常規的超外差電臺的接收機類似.射頻前端的主要功能是將射頻信號下變頻為適合A/D轉換器采樣的帶寬及中心頻率適中的中頻信號,這樣大大減輕后續的 A/D轉換器采樣以及信號處理負擔。中頻信號經帶通采樣后,再通過FPGA中的DDC以及數字信道化,進一步降低信號處理速率。使得后續數字信號處理更容易。

2 系統實現

2.1 前端高速采樣模塊

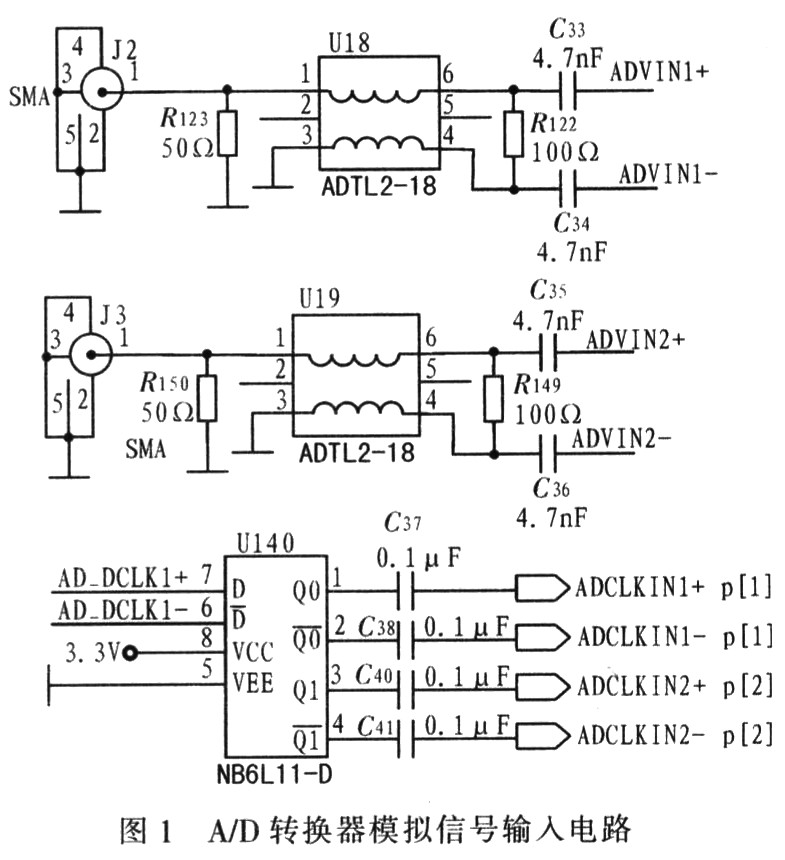

ADC08D1000是雙通道低功耗8 bit A/D轉換器,單通道最高采樣頻率達1.3 GHz,全功率帶寬1.7 GHz,1.9 V電源供電.每個通道差分輸入。其模擬輸入包括采樣時鐘以及2路采樣信號,由于均為差分輸入,所以要通過變壓器對單端輸入的信號進行轉換。由于該A/D轉換器的輸入阻抗為100 Ω,所以差分輸出端接100 Ω電阻,將輸出阻抗轉為50 Ω差分阻抗。A/D轉換器模擬輸入電路如圖1所示。由于A/D轉換器為差分輸出,其100 Ω匹配電阻應盡量靠近FPGA引腳放置。

2.2 FPGA的信號處理單元

FPGA選擇Altera公司的StratixII系列器件,該系列FPGA特點:采用“自適應邏輯模塊”(ALM)構架優化FPGA的性能及資源利用率;高速DSP模塊(最高達370 MHz),實現專門的乘法、乘加運算及有限脈沖響應(FIR)濾波器;最多有16個全局時鐘,支持動態時鐘管理以降低用戶模式時的功耗;最多有12個鎖相環(PLL)。根據該設計的數據處理要求,以及估算處理所需的資源,選用EP2S90F1020C3型FPGA。

2.3 系統原理框圖

A/D轉換器的采樣速度為600 MHz,A/D轉換器內部通過DMUX輸出300 MHz奇偶兩路送至FPGA,FPGA內部通過LVDS模塊轉換為單端信號,然后進行數字下變頻(DDC)處理。需注意,A/D采樣得到的數字信號為偏移二進制類型,需轉換為補碼形式,以便后續處理。

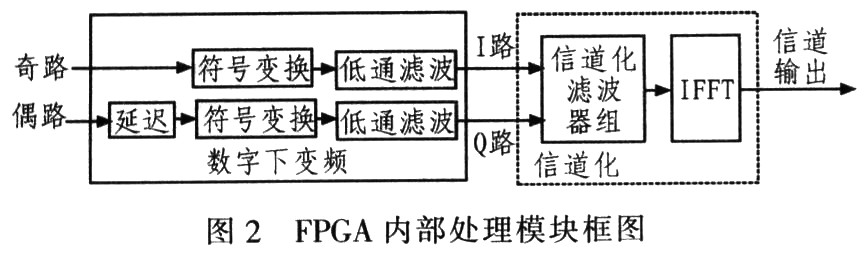

DDC后得到的基帶信號進入信道化繞行電感器濾波器組完成信道化處理,可得到32路子帶信號,此時每個子帶信號的速率降為300~32 MHz,從而大大減輕后續信號處理負擔。圖2是FPG插件電感A內部處理模塊框圖。

2.3.1 數字下變頻DDC

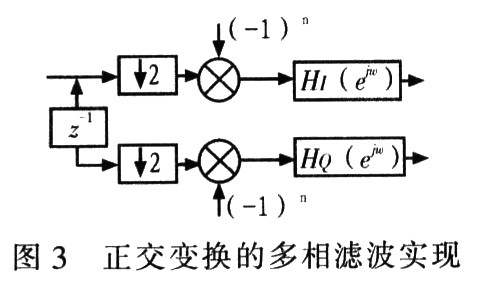

A/D轉換器的輸出信號為LVDS形式,進入FPGA后需轉換為單端信號。采用 Altera公司提供的模塊完成信號轉換。由于A/D轉換器采用偏移二進制,需轉換為補碼形式。數字下變頻是將高速率信號變成低速率基帶信號,以便進一步作信號處理。典型的數字下變頻采用乘法器和NCO實現,其缺點:A/D轉換器需在高頻下采樣數字化;當采樣速率很高時,后續數字低通濾波則成為瓶頸,特別是當濾波器階數很高時:低通濾波后抽取,這意味著有很多經下變頻和低通濾波后的數據都未被利用,浪費大量運算結果,運算效率低。因此,這里提出一種基于多相結構的高效寬帶數字下變頻結構,如圖3正交變換的多相濾波實現圖3所示。

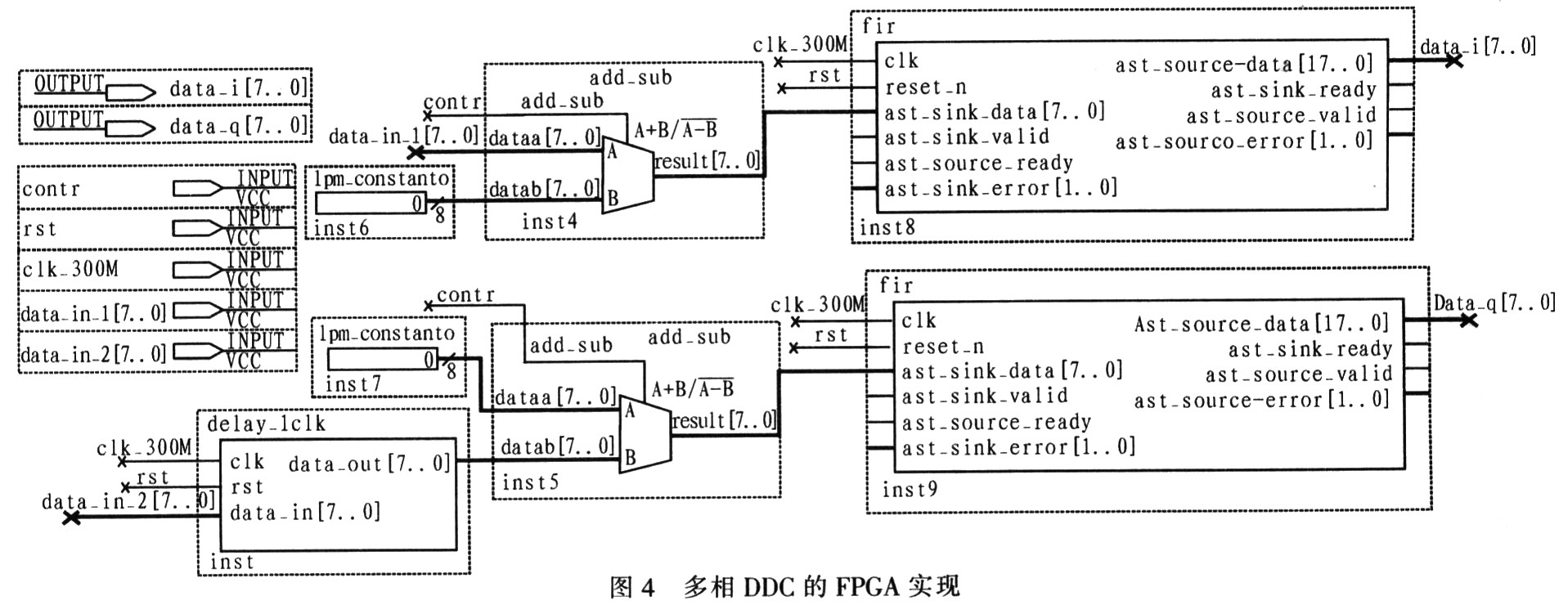

具體實現:2倍抽取在A/D轉換器內部通過DMUX完成,然后由符號轉換將輸人信號正負交替輸出,利用加法器實現,加減可控制。

需輸出原數據時,加減控制設為加法;需輸出反相數據時,則設為減法,輸出數據為零減去原數據。FPGA實現如圖4所示。

2.3.2 多相信道化濾波器組

經下變頻得到I,O兩路信號,為得到較高的頻率分辨率,采用電感器用途信道化法。該方法的基本原理是將輸入的全帶信號進行頻帶分割,即把接收到的信號頻段分解成若干個不同頻段(又稱子頻段或子信道),然后分別處理各子段。為得到更高的頻率分辨率,各子頻貼片電感器段可分別再進行第2次分割、第3次分割,直到滿足頻率分辨率的要求。由于該設計的接收機工作在中頻,因此只需1次分割即可。

假設偵察系統接收的中頻帶寬為300 MHz,A/D轉換器采樣速率為600 MHz,帶通采樣,無模糊帶寬為300 MHz,周期延拓后,中頻帶寬(300 MHz)落在其中的一個周期內,因此不會產生頻率混疊現象。無模糊帶寬(300 MHz)分為32個信道,輸入分為實部和虛部共模電感器。各信道帶寬是9.375 MHz(300/32)。該系統設計采用基于DFT多相濾波器組的信道化濾波器技術,實現數字信道化濾波器。由于采用預先抽取方式,降低濾波運算的運算量。而IDFT可利用FFT實現。因此系統的數據率降低,實時性能很高。

大功率電感廠家 |大電流電感工廠