引言

電源時序控制是微控制器、FPGA、DSP、 ADC和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數字I/O軌上電前對內核和模擬模塊上電,但有些設計可能需要采用其他序列。無論如何,正確的上電和關斷時序控制可以防止閂鎖引發的即時損壞和ESD造成的長期損害。此外,電源時序控制可以錯開上電過程中的浪涌電流,這種技術對于采用限流電源供電的應用十分有用。

本文討論使用分立器件進行電源時序控制的優缺點,同時介紹利用ADP5134內部精密使能引腳實現時序控制的一種簡單而有效的方法ADP5134內置2個1.2-A 降壓調節器與2個300-mA LDO。同時,本文還列出一系列IC,可用于要求更高精度、更靈活時序控制的應用。

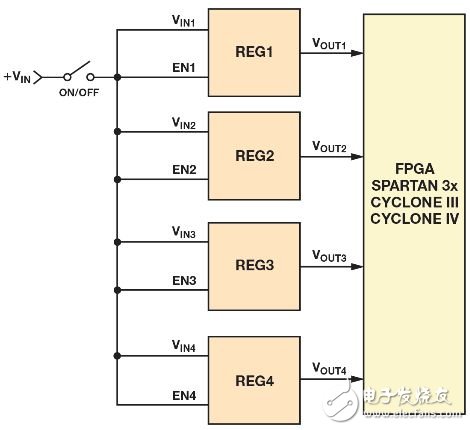

圖1 所示為一種要求多個供電軌的應用。這些供電軌為內核電源(VCCINT)、I/O 電源(VCCO)、輔助電源(VCCAUX)和系統存儲器電源。

圖1. 處理器和FPGA 的典型供電方法

舉例來說,Xilinx Spartan-3AFPGA 具有一個內置上電復位電路,可確保在所有電源均達到其閾值后才允許對器件進行配置。這樣有助于降低電源時序控制要求,但為了實現最小浪涌電流電平并遵循連接至FPGA 的電路時序控制要求,供電軌應當按以下序列上電VCC_INT → VCC_AUX→ VCCO。請注意:有些應用要求采用特定序列,因此,務必閱讀數據手冊的電源要求部分。

使用無源延遲網絡簡化電源時序控制

實現電源時序控制的一種簡單的方法就是利用電阻、電容、二極管等無源元件,延遲進入調節器使能引腳的信號,如圖2 所示。當開關閉合時,D1導電,而D2仍保持斷開。電容C1充電,而EN2處的電壓根據R1和C1確定的速率上升。當開關斷開時,電容C1通過R2、D2和RPULL向地放電。EN2處的電壓以R2、RPULL和C2確定的速率下降。更改R1和R2的值會改變充放電時間,從而設置調節器的開啟和關閉時間。 大功率電感廠家 |大電流電感工廠