通用異步接收/發送器(UART)是一種通用串行數據總線,用于異步通信,可以實現全雙工通信。UART IP核是用在外部設備和Atera FPGA芯片上的SOPC間進行串行通信的一種實現方式。它可以替代RS-232實現芯繞行電感片與外設的輸入/輸出(I/O)操作。

GPS RTK(Real Time Kinematic)可以即時提供厘米級的定位解。在進行動態定位時,基準站將精確已知的GPS坐標和觀測數據實時用微波鏈路傳給流動站,在流動站實時進行差分功率電感器處理,得到基準站和流動站坐標差;坐標差加上基準站坐標得到流動站每個點坐標。基準站向終端用戶接收機提供的信息包括對GPS衛星鐘、星歷數據、用戶測量偽距和載波相位等參數的修正。

本文所用的信號處理板可以作為GPS RTK基站使用,可以與其他基站組網接收差分修正數據定位或者本身的高精度單點定位輸出定位結果和差分修正數據。作為基準站,不僅要實時輸出精確定位信息,而且需要與外界進行差分數據交換。由于同一時間需要大量持續差分數據的輸入與輸出和用戶控制指令的輸入,設計采用了3個串口。

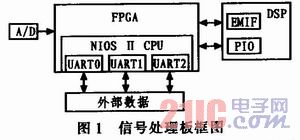

1 硬件結構

信號節能燈電感器處理板為FPGA+DSP結構,具有多路A/D、D/A轉換器件。中頻信號經A/D采樣后進入FPGA完成去載波,PRN碼相關運算,IQ變換等操作后由DSP芯片進行定位解算。通過串口輸入的用戶控制指令任意選擇串口對GPS定位結果的輸出和GPS差分修正數據的輸入輸出。

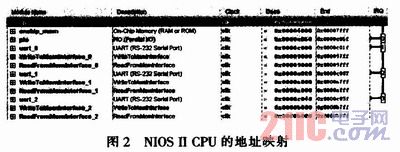

FPGA芯片上配置了3個串口,分別為UART0、UART1、UART2,由SOPC Builder分配相對應的存儲映射空間和中斷請求。每個模塊均使用默認的基地址,并分別設定UART0、UART1、UART2的數據輸入中斷請求號為IRQ1,IRQ2,IRQ3。另外,DSP芯片可能在任意時刻通過3個串口發送不同數據。

如果DSP對每個串口發送數據時均向NIOS II CPU發出中斷申請,則需要3根PIO管腳,占用太多針腳資源。本實現方案通過增加個串口控制寄存器,僅占用1根PIO管腳。

同時,對和DSP芯片進行交互控制的PIO信號分配中斷請求號為IRQ0。

每個UART口都有輸入、輸出兩塊RAM作為緩存,數據位寬為16bits。其中,串口輸入緩存命名為ReadFromMemInterface,串口輸出緩存命名為WriteToMemIntedace(見圖2)。需要注意的是實際傳輸數據時,外部設備的串口參數的數據位長度設置為8 bits,因此需要在串口的軟件處理進行字與字節的轉換。

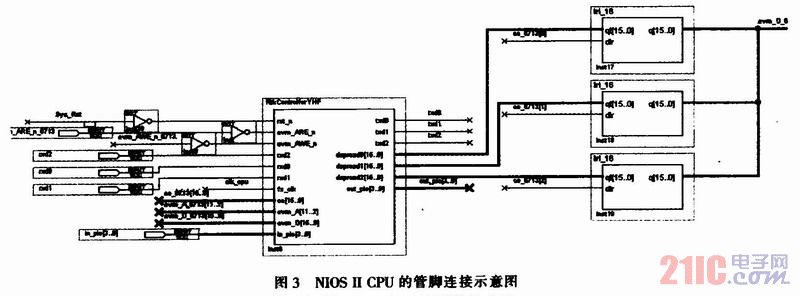

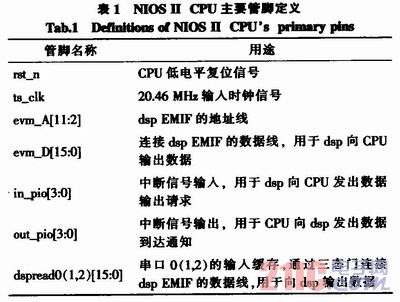

圖3是NIOS II CPU在Quatus中的連線示意圖,即位于中心的inst6模塊。該CPU主要管腳定義如表1所示。

值得說明的是,ts_clk輸入時鐘20.46 MHz即為NIOS IICPU的時鐘頻率,串口波特率為115 200 bps,可由該時鐘分頻得到。DSP6713的EMI工字電感F為輸入輸出雙向32位,在本設計中串口部分僅使用低16位,使用三態門來控制數據流向。三態門輸入輸出的使能信號是dsp給出的ce空間使能信號ce_6713。

串口輸入數據先由NIOS II CPU寫入每個串口的輸入緩存,當滿足條件時由out_pio管腳向dsp發出中斷,用以告知其可以讀取相應串口的數據了,緩存的數據由dspread0傳遞至三態門tri_16.dsp讀取時三態門為dsp輸入方向,dsp的EMIF數據線evm_D隨即出現數據,配合EMIF地址線evm_A即可完成串口輸入數據向dsp傳遞;當dsp工字電感有數據要經串口輸出時,數據由dsp的EMIF數據線evm_D輸入,dsp通過in_pio向NIOS II CPU發出中斷信號,請求發送數據。詳細的發送接收流程見下文。

2 軟件設計

NIOS II CPU的控制代碼部分分為主函數和各種中斷響應函數。在主函數里完成寄存器初始化、各串口數據輸出的任務。串口的中斷響應函數則主要完成數據的輸入任務。

為了便于FPGA和DSP之間的控制信息交換,每個串口設有地址固定的長度各為32位(4字節)的輸入和輸出兩個控制寄存器。通過對各標志位的讀寫操作即可實現系統對各串口的控制。串口的輸入控制寄存器定義見表2,輸出控制寄存器與之類似。 大功率電感廠家 |大電流電感工廠