關鍵字:ADSP210共模電感62 雷達 信號處理

ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM,并集成了I/O設備。借助它的片內指令緩存,處理器可以在一個時鐘周期內執行每一個指令。AD模壓電感器SP2106x SHARC體現了數字信號處理器的一個新的集成標準,它把一個高速運行的浮點DSP主處理器與集成的片內部件結合在一起,包括一個主機接口、DMA控制器、串口和連接口。由于它處理速度快、便于DSP多處理系統的連接和通信,目前已在更多的領域獲得了開發和應用 1 。但如何對基于ADSP2106x的處理系統進行調試是人們在應用該芯片時必須解決的關鍵問題。本文提出了一種簡單易行的測試方法,并在基于ADSP21062的雷達信號處理系統調試中獲得了成功,驗證了該方法的可行性。

1 雷達信號處理系統設計簡介

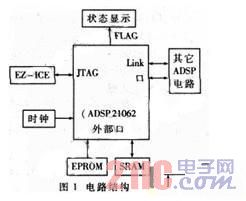

我們應用ADSP21062處理器設計了一個雷達信號處理系統。此系統可以獨立地進行工作,也可通過Link口與其它DSP進行通信。ADSP21062利用JTAG接口與EZ-ICE仿真器連接,實現對系統的仿真和測試。系統的電路結構見圖1。

EZ-ICE仿真器應用IEEE1149.1 JTAG測試標準,監視和控制目標板處理器的工作。EZ-ICE仿真器的測試頭通過一個14針的連接頭與目標板處理器的CLKIN (可選)、TMS、TCK、TRST、TDI、TDO、和GND信號相連。在電路板上設計了一個14針的電感器鐵芯接口,其信號的接口如圖2所示。

2 電路的測試

電路測試主要應用EZ-ICE仿真器。該仿真器插在PC機的ISA槽中,通過JTAG口與ADSP21062處理系統相連,可在PC機的顯示器上利用Emulator控制界面對DSP系統運行情況進行實時監控。ADSP2106x提供了模擬(Simulator)和仿真(Emulator)兩套軟件,它們的界面完全相同,只是一個不需要硬件,一個需要硬件。測試程序可先由Assembler匯編器匯編,再經Simulator模擬通過。最后在Emulator界面控制下可以裝入由匯編生成的可執行文件(.EXE文件)和匯編的結構文件(.ACH文件),實現對硬件的測試和仿真。

2.1 硬件測試的基本操作

對硬件測試時,先對存儲器的內部控制、狀態寄存器和存儲器做簡單的操作,確定EZ-ICE仿真器與處理器的通信正常。

對寄存器的操作一般有兩種:位操作和字操作 2~3 。

(1)位操作:寄存器的位塑封電感操作主要用于BIT SET,BIT CLR。

例如:BIT SET MODE2 0x00000001

BIT CLR MODE2 0x00000001。

以上操作將MODE2的第一位置位或清除,而不影響到其它位。

(2)字操作:寄存器的字操作用DM()尋址指令。

例如:R0=0x00000001;

DM(SYSCON)=R0。

以上操作將SYSCON的第一位置位,其它位清除。

對存儲器的操作采用DM()指令尋扯,在指令中加入立即數、寄存器Rx(內容為尋址值)、基址(Ix)和變址(Mx)可實現直接尋址、間接尋址和變址尋址。

例如:R0=0x23;

DM(0x00030000 =R0。

以上操作將0x23放入0x00030000的地址內。

2.2 系統運行測試

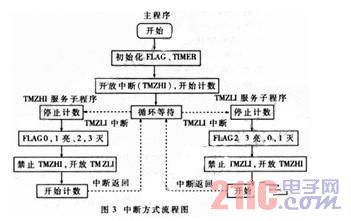

設計一個對FLAG位的四個指示燈的操作,讓其交替地閃爍,來檢驗ADSP21062處理器是否能夠正常運行。程序采用中斷方式,利用定時器溢出時產生兩個中斷TMZHI和TMZLI。一個中斷的服務程序設置FLAG0,1的指示燈亮,FLAG2 3的指示燈滅;另一個中斷服務程序設置情況相反。兩個服務程序交替執行,交替的間隔由定時器的初值確定。程序流程圖見圖3。

由于處理器在系統復位時MODE2寄存器被清除,使FLAG管腳作為輸入,處理器不能改變其狀態。所以主程序需對其初始化,使FLAG管腳作為輸出,然后才能在ASTAT寄存器中改變FLAG的狀態。同樣,對定時器也要進行設置。

(1)定時器的設置:

BIT SET MODE1 0x1000;(開放全局中斷)

BIT SET MODE2 0x20; (開放定時器一體成型電感器)

BIT SET IMASK 0x10; (開放TMZHI中斷)

(2)FLAG位的設置:

BIT SET MODE2 0x78000; (設置為輸出)

BIT CLR ASTAT 0x180000; (FLAG0 1亮)

BIT SET ASTAT 0x600000; (FLAG2 3滅)

此程序可通過JTAG仿真測試,用通用編程器將此程序寫入EPROM,然后讓系統單獨工作,來驗證系統能否正常引導和工作。上電后四個指示燈交替閃爍,經驗證系統順利地完成了引導,并且工作正常。 大功率電感廠家 |大電流電感工廠