本文從對比兩顆分立MCU與單芯片雙核MCU開始(以LPC4350為例),展開介紹了非對稱雙核MCU的基礎知識與重要特點。接下來,重點介紹了核間通信的電感器市場需求概念與幾種實現方式,尤其是基于消息池的控制/狀態通信。然后,對內核互斥、初始化流程等一些重要的細節展開了論述。最后提出了雙核任務分工的兩種應用模型,并分別舉例。

背景與基本概念

在開發MCU應用系統時,如果單顆MCU無法滿足系統的要求,一個很普遍的做法就是使用兩顆或更多的MCU,把一部分“雜項工作”分配給另一個有“助理”性質的低端MCU來完成。但是,采用兩顆MCU,缺點也很明顯,尤其是在芯片與PCB成本、系統可靠性及功耗方面都有先天的不足。此外,若采用了不同塑封電感器架構的MCU,還要面臨需要不同的開發工具與開發人員的挑戰。如果換一種思路,讓MCU內部包含兩個內核,其中一個用于主控,另一個用于協控,并且它們主控與協控在架構上能夠向下兼容、高效通信,則在很多場合下都可以既保持多機系統的強大,又能避免多機系統的不足。

事實上,這即是“非對稱多處理器(簡稱AMP)”架構的特點。AMP是與“對稱多處理器(簡稱SMP)”相對的架構,后者各處理器有一致的編程模型,并且在分配工作時主要以均衡為原則。而AMP的優點在于精細的任務分工,靈活地適應不同情景,物盡其用,以最佳地平衡成本、性能與功耗。此外,AMP的編程難度也更低。因此,在MCU應用領域,AMP較SMP更為適合。

與獨立的雙MCU相比,AMP架構有很多優點。其中相當關鍵的就是,再添加一個內核的代價遠比添加一個獨立的MCU要低,尤其是當兩個內核架構相似時,甚至僅相當于在現有硅片上再添加一兩個UART。另一方面,兩個內核可以有相同的主頻,并且可以通過總線矩陣平等地訪問片上資源。而在分立的雙MCU方案中,協控MCU的主頻常常遠低于主控,并且雙方使用低速的串行鏈路通信。

接下來,我們以恩智浦(NXP)半導體公司新推出的LPC4300系列為例(尤以LPC4350型號為代表),對AMP MCU進行簡單介紹。

非對稱雙核MCU的特點

AMP MCU一般用于相對大型的系統,這些系統對功能和性能都有較高的要求。在功能上,應支塑封電感器持較多的外設。LPC4350片載2個高速USB、2個CAN、工業以太網、圖形LCD控制器,以及SDHC等接口;外加一些獨有的邏輯可配置外設以及眾多傳統外設,適用于工控、能源、醫療、音頻、車載、電機、監控等眾多行業產品的開發。

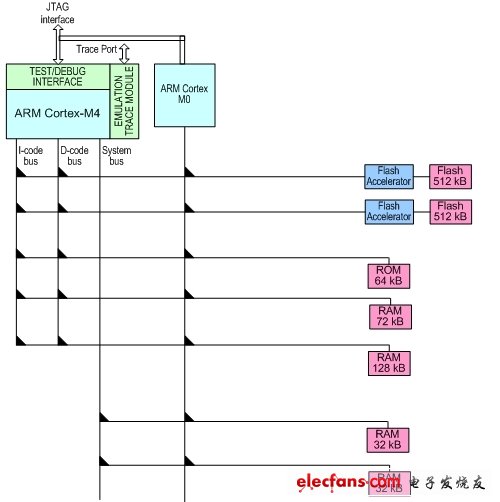

性能的改善則是AMP MCU的靈魂。內核、存儲器,以及總線架構對于性能有著至關重要的影響。圖1展示了LPC4350的實現方式。

圖1:LPC4350的內核、存儲器以及總線連接圖

首先是內核的選擇。LPC4350基于32位的ARM Cortex-M4和Cortex-M0內核(以下簡稱M4和M0),兩個內核均可在高達204MHz的主頻下執行代碼。其中,M4以信號處理和浮點運算能力見長,勝任很多原先要采用DSP才能滿足的應用,并且繼承了Cortex-M3的控制能力;另一方面,M0以其成本、能效和處理能力的壓倒性優勢,正迅速吸引開發人員從8/16位架構向上過渡。更重要的是,M4完全向下兼容M0,使用同一套開發工具即可開發、調試。

其次是存儲器的容量和組織方式。LPC4350配備多達264KB片上RAM,并且這些RAM被劃分共模電感器成4組,每組連接一條單獨的總線,而并非沒有分塊。如若不然,則會出現兩個核競爭使用同一塊RAM的情況——性能反而還不如只用單個內核!進一步,LPC4350還有兩條總線連接到外部擴展的并行和串行存儲器,故總共有6個獨立的存儲器地址空間——LPC4350無片上閃存。對于有片上閃存的型號,片差模電感上閃存也分為兩塊。

最后是總線架構。LPC4350內部有一個八層總線矩陣。它如同一組縱橫開關,可以把CPU與包括存儲器在內的眾多從設備通過總線任意連接。合理分配總線接通關系,避免多個主設備(如CPU和DMA)同時訪問相同的存儲器或外設,可以最大地保證各條數據流并行不悖,從而可以充分發揮性能上的優勢。

內核間通信

內核間的通信可分為兩類:一類是控制與狀態信息的通信,另一類則是數據通信。前者一般不攜帶數據,但往往有較高的實時要求;后者則主要是各類數據緩沖區,通常實時性要求偏低但數據量大。控制/狀態通信有較大的通用性,并且與任務間的同步較為相似。這類通信適合由系統軟件實現并提供編程接口。數據通信則往往與具體應用相關較大(尤其是在數據結構上),需要量體裁衣。在實現時,適合由應用軟件定義各種數據結構。 大功率電感廠家 |大電流電感工廠