1.引言

USB(Universal Serial0603貼片電感 Bus,通用串行總線)以其無需配置、即插即用等特性獲得了廣泛的應用。2004年提出的USB2.0標準,傳輸速度最大能夠達到480Mbps.但在USB3.0標準中,它的最大傳輸速度幾乎是傳統USB2.0傳輸速度的10倍,達到了5.0Gbps,被定義為“超高速U S B接口”.本文基于CYPRESS的FX3系列USB3.0芯片,對USB3.0總模壓電感器線進行研究開發。

2.USB3.0接口芯片概述

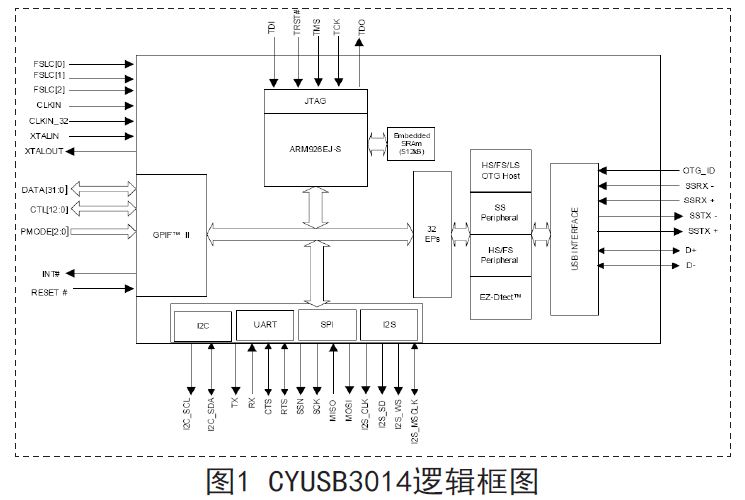

賽普拉斯的EZ-USB FX3是新一代的USB3.0外設控制器,具有高度集成的靈活特性,允許系統設計者將USB3.0添加至任何系統。本文采用的是FX3系列USB3.0芯片CYUSB3014.

FX3是完全兼容USB3.0 V1.0和USB2.0規范的,集成的USB2.0 OTG控制器允許芯片作為主從設備使用。另外,它還支持一些常用的外設接口,如SPI,I2C,UART和I2S可以與外部設備進行通信。

FX3具有一個可進行完全配置的并行通用可編程接口GPIF II,它可以與任何處理器、ASIC或是FPGA連接。它可以輕松無縫地連接至多種常用接口,比如異步SRAM、異步和同步地址數據復用式接口、并行ATA等等。EZ-USB FX3集成了USB3.0和USB2.0物理層(PHY)以及32位ARM926EJ-S微處理器,具有強大的數據處理能力,并可用于構建定制應用。

3.系統整體設計

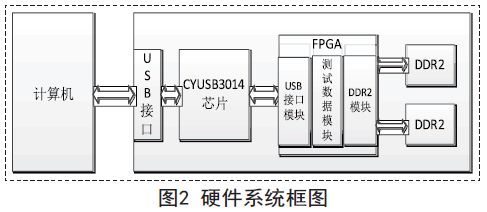

本系統設計主要由軟件工字電感器部分和硬件部分組成。軟件部分主要包括三大部分:PC機應用程序、FX3固件程序、FPGA程序。硬件部分主要由FPGA、USB3.0芯片和DDR2組成,硬件的系統框圖如圖2所示。本文主要完成了硬件、PC機應用程序和FPGA程序的設計。

FX3固件程序使用的是Cypress的SDK開發包的固件程序。

3.1 DDR模塊設計

與FPGA相比,USB3.0接口是一個高速的接收單元。在不同工作速度的系統之間,數據緩存是不可或缺的部分,一般來說,使用FIFO基本可以使各系統工作在自己的時鐘頻率下,而不需要反復的互相握手信號就能進行數據的交流。本文設計的數據是保存在計算機上,由于各計算機的硬件配置可能會不一樣,我們設計了DDR2虛擬FIFO模塊來進行數據緩存,為批量傳輸時能夠提供足夠的緩存,不用擔心為緩存不夠電腦來不及存取數據造成數據丟失。

本系統選用兩片MT47H64M16HR,兩片DDR并聯控制總線和地址總線,總存儲容量達到2Gbit,讀寫寬度都為16bit,它具有豐富的資一體電感源,足夠滿足本系統的需要。

3.2 USB3.0接口設計

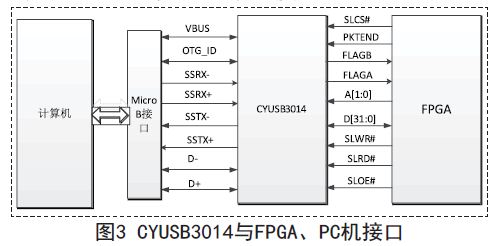

與USB2.0不同的是,USB3.0在與計算機通訊時,它有自己專用的數據通路,專用的數據發送線路和獨立的數據接收線路,即圖3中四線差分信號SSRX+/-和SSTX+/-,從而可以真正的實現全雙工。同時,USB3.0還兼容了USB2.0的D+/-信號接口,從而可以與USB2.0無縫連接。使用從器件FIFO接口與FPGA鏈接,傳輸速度能達到可達到320MBps.圖3為USB芯片與FPGA和PC機的電路連接。

3.3 FPGA邏輯設計

FPGA是整個系統的核心,它需要產生測試數據并將數據存儲到DDR2中,以及將DDR2中讀出的數據轉移到CYUSB3014大的內部FIFO中,因此它主要由如圖2內部所示模塊構成。

3.3.1 USB接口模塊

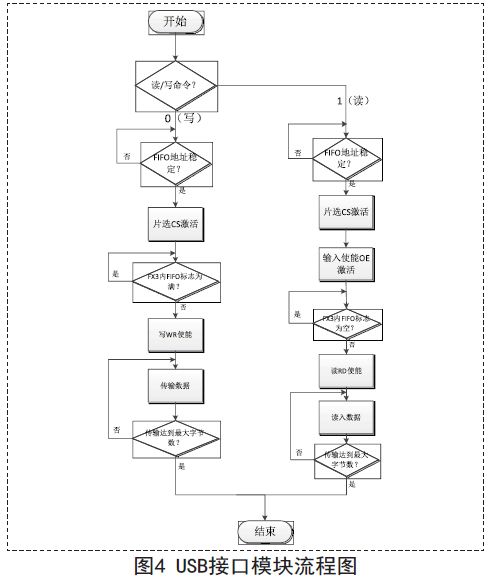

USB接口模塊主要處理讀寫命令。讀寫命令需要計算機通過USB控制傳輸,傳遞到CYUSB3014中,再由CYUSB3014將具體的命令轉化為電平信號送到FPGA的IO口。USB接口模塊根據UART_RX上的電平信號,判斷出是讀命令還是寫命令,最終產生CYUSB3014的片選CS、使能OE、讀/寫控制等有效信號。

當為寫命令時,CYUSB3014需要將從DDR2中讀取的數據發送出去;當為讀命令,讀取CYUSB3014傳遞過來的數據,流程圖如圖4所示。

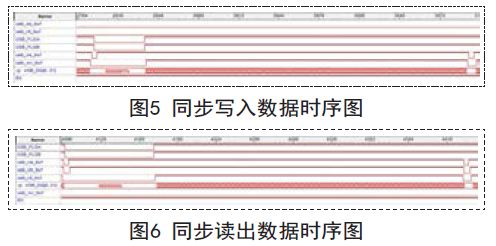

圖5、圖6分別為同步寫入和讀出數據的時序圖。由于讀寫最大包為1024字節,所以實際每一包傳輸需要256個周期。圖中的輸入/出DQ數據為測試數據模塊和PC機產生的測試數據,RX即UART_RX信號。

3.3.2 測試數據模塊

當計算機電感器生產向FPGA發出讀命令時,FPGA產生測試數據。32位數據,高16位為0,低16位循環計數,發送一個周期后,自動清零。 大功率電感廠家 |大電流電感工廠