摘要:基于目前流行的TSPC高速電路,利用TSMC90nm 1.P9M 1.2V CMOS工藝設計了高速、低壓、低功耗32/33雙模前置分頻器,其適用于WLAN IEEE802.1la通信標準。運用Mentor Graphics Eldo對該電路進行仿真,仿真結果顯示,工作在5.8GHz時功耗僅0.8mW,電路最高的工作頻率可達到6.25GHz。

關鍵詞:雙模前電感生產置分頻器 單相時鐘 高速度 低功耗

0 引言

隨著移動通信技術的迅速發展,對射頻電路的高速、低功耗要求日益增長。基于鎖相環(PLL)結構的頻率合成器是收發機前端電路的重要組成部分,對為混頻器提供純凈的本振信號,具有重要地位。在PLL中,壓控振蕩器(VCO)和前置分頻器(Prescaler)是工作在最高頻率的兩個模塊,它們是限制PLL工作頻率的主要瓶頸,因此提高前置分頻器的工作速度是解決限制PLL工作頻率上限的一個關鍵因素。為了滿足高頻通信的要求,必須對前置分頻器和VCO進行高速、低功耗的優化設計。

雙模前置分頻器以D觸發器為主要單元。近年來涌現了很多不同結構的高速D觸發器。第1種是靜態SCL結構,由ECL電路結構演變而成。與傳統的靜態分頻器相比,由于它的擺幅較小,所以工作速度快。但是典型SCL結構的2分頻電路包括尾電流源在內至少需要18個MOS管,MOS管無法做到小尺寸,導致輸入電容很大甚至超過了管子本身的電容,所以SCL分頻器功耗較高。第2種是動態的TSPC(單相時鐘)結構,它采用單相時鐘的TSPC技術使構成分頻器的元件數目減少,可以提高電路的工作速度,同時這種電路的功耗極低,所以經常在前置分頻器中采用。TSPC分頻器的不足是噪聲性能不佳,因為動態單端結構比SCL結構更容易受噪聲的影響。第3種是注鎖式(iniected-locked)電路,由于要使用電感器,因而它的體積過大且工藝難度高,很少被應用。具體采用哪種電路結構應視情況而定。

本文采用動態TSPC結構,利用TSMC 90nm 1P9M 1.2VCMOS工藝,設計了一個適用于WLAN IEEE802.11a標準的雙模前置分頻器,具有高速、低壓、低功耗的特點。

1 電路設計

1.1 電路總體架構

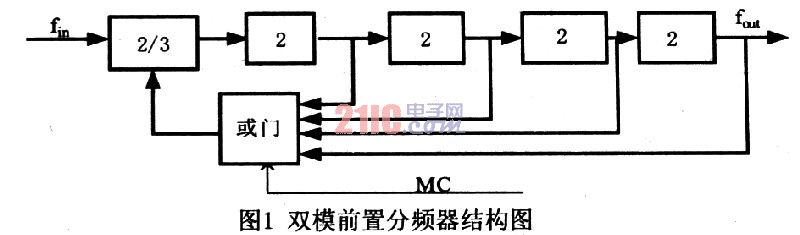

雙模前置分頻器的基本結構如圖1所示,包括三個部分:同步2/3分頻器,由異步除2分頻器構成的分頻器鏈,以及反塑封電感器饋部分。控制信號MC控制分頻比,當MC=1時為32分頻,當MC=O時為33分頻。

圖l雙模前置分頻器結構圖

本設計基于上述傳統結構,通過減少高頻同步分頻器單元中MOS管的個數,達到降低功耗的目的。

1.2 同步分頻器設計

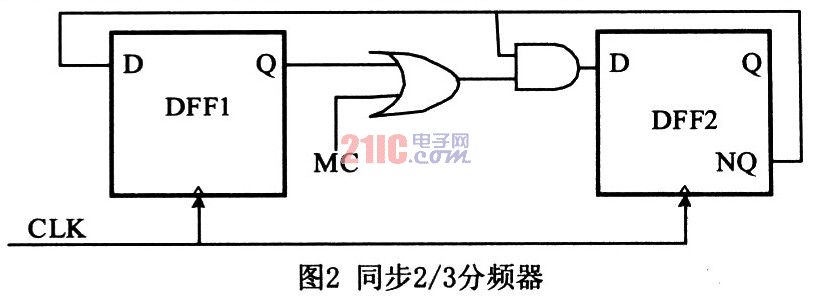

同步2/3分頻器的結構框圖如圖2所示,它是整個分頻器工作頻率最高的部分,亦是決定前置分頻器速度和功耗的關鍵部分。

MC為邏輯高電平時,電路實現2分頻;MC為邏輯低電平時,電路實現3分頻。采用同步2/3分頻器,大大減少了工作在高頻部分MOS管的數目,從而同步部分的功耗有所下降。同時將“與”門設計在D觸發器中。這種集成“與”門的觸發器不但簡化了電路設計,而且避免了單獨設計邏輯門所帶來的寄生參數的影響,減少了速度損失,從而很好地緩解了工電感器的參數作速度和功耗之間的矛盾。

1.3 優化功耗

從以上的分析可以看出,電路最大的功耗來自同步2/3一體電感器分頻器,但無論是同步2/3分頻器還是異步分頻器鏈都必須采用D觸發器,因此設計好高速低功耗的D觸發器是影響整個分頻器速度和功耗的關鍵。

圖3為常用的Yuan-Svensson型D觸發器(下降沿觸發),這種電路采用動態CMOS技術,從左至右由一個N-C2MOS級,一個P-PrechargeCMOS級和一個P-C2MOS級組成。相對于傳統的靜態分頻器,它的各項性能已經有了明顯的改善,但是由于大多數MOS管既是前級的負載管又是后級的驅動管,每一級三個MOS管疊加帶來了大的RC延遲,所以就算減小其尺寸也不能提高速度。為此我們對圖3中的C2MOS電路進行改進,用鐘控偽PMOS反相器代替N-C2MOS,這樣MOS管的數目、負載電容都有減小。同樣用鐘控偽NMOS反相器代替PC2MOS,構成圖4所示的動態有比鎖存器,當時鐘信號為低(高)電平時鎖存器工作在求值(保持)模式,與Yuan-Svensson結構的D觸發器相比具有更低的RC,因此減小了功耗和傳輸延遲。