過去,FPGA設計人員考慮的是時序和面積使用率。但是,隨著FPGA正越來越多地取代ASSP和ASIC,設計人員期望開發功率較低的設計并提供更加精確的功率估計。最新FPGA分析軟件能提供一種精確和靈活的手段來模擬各種工作環境下的功耗。

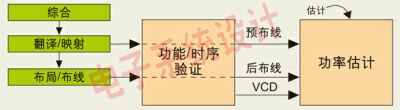

與功能和時序驗證類似,功率分析以并行驗證的形式對設計流程進行跟蹤(見圖1)。早期的功率分析依賴于簡單的利用率和由設計者用“假設分析”方法提供的信號活性評估。后來,由于可以獲取布局后(post-layout)器件信息和門級仿真記錄的信號活性,功率估計變得更加精確了。

FPGA功率計算器可評估器件功耗,使設計者能夠導入布局和布線設計,并指定諸如電壓、溫度、工藝變化、氣流、散熱片及資源利用率、活性和頻率等參數。應用這些參數可以在不同的設計環境下形成盡可能精確的模型。

圖1:功率估計并行于傳統的驗證流程。

基本功耗計算

大多數FPGA功率分析工具可報告功耗的動態(AC)和靜態(DC)部分。靜態電流由器件的漏電流組成。靜態電流/功率與器件的溫度、工藝、電壓參數和條件有關。它在很大程度上取決于溫度,溫度與電路板及器件的熱特性相關。靜態功耗也是所有電源上的漏電流。

功耗的動態部分為所使用的資源在轉換時的功耗。動態扁平型電感部分的功耗直接與工作頻率(資源在該頻率下工作)和使用的資源數量成正比。

DC功率由下面的方程得出:總DC功率(器件)= A×eBT

其中:A是與參數相關的工藝,B是溫度系數,T是器件的結溫。

AC功率由下面的方程得出:總AC功率(資源) = Kr×fMAX× AF×Nr

其中:Kr是針對資源的功率常數(單位為mW/MHz)。fMAX是正在使用的資源的最大頻率。頻率用MHz量度。AF是資源組的活性因子。活性因子是切換頻率的百分比。Nr是設計中使用的資源數目。

FPGA布線互連是整體功耗的主要來源,功耗與金屬層的電容和轉換率成正比。

活性因子(AF%)被定義為頻率(或時間)的百分比,在該頻率下信號被激活或者轉換輸出。大多數與時鐘域相關的資源以某頻率的百分比運行或轉換。功率分析工具的用戶可以手工將這些參數以百分比形式輸入,或者根據仿真結果導入活性因子。可針對每個布線資源、輸出或PFU計算出AF。如果未提供仿真結果,則對于一個占器件資源30%到70%的設計,通常建議AF%在15%到25%之間。AF(通常從仿真結果導入)的精確性取決于時鐘頻率,設計的激勵信號和最終輸出。

器件的I/O消耗大量的功率,對于一個指定設計可以將其配置成串行或混合結構。由用戶提供的信號(輸入情況)或作為設計的輸出(輸出情況)的信號決定了混合I/O的狀態。I/O轉換速率定義了它們的狀態。下列方程定義了輸出的轉換速率,用MHz表示。

轉換速率(MHz) = 1/2×fMAX×AF%

其它環境因素,如電路板的面積、散熱片和氣流都是計算動態和靜態功耗時的要素。

管理功耗

現今最關鍵的設計要素之一是必須降低系統的功耗,特別是對于手持設備和電子產品而言。用戶可以利用一些FPGA設計技術來有效地降低整個系統的功耗,包括:插件電感器

1. 降低工作電壓。

2. 在指定的封裝溫度限制范圍內運作。

3. 使用優化的時鐘頻率,因為動態功率直接與工作頻率成正比。設計者必須明確,如果設計的某部分可以以較低速率時鐘控制,那將會降低功耗。

4. 減小設計在器件中的跨度,緊密放置的設計可使用較少的布線資源以降低功耗。

5. 可能的話,減小I/O的電壓擺幅。

6. 可能的話,使用優化的編碼。例如16位的二進制計數器平均只有12%的活性因子,7位的二進制計數器平均有2電感生產廠家8%的活性因子。另一方面,7位線性反饋移位寄存器的可以以50%活性因子轉換,這會導致較大的功耗。每個時鐘沿僅有一位改變的格雷碼計數器所消耗的功率最少,同時活性因子將低于10%。

7. 利用以下方法盡可能減小工作溫度:使用散熱性能較好的封裝,例如具有較低熱阻抗的封裝;在PCB上的器件電容電感周圍放置散熱片和散熱層;采用更好的氣流技術,如機械氣流導管和風扇(系統風扇和器件風扇)。

典型的功率分析方案

大功率電感廠家 |大電流電感工廠