在便攜式數(shù)字衛(wèi)星通信系統(tǒng)中,為了擴大傳輸容量和提電感器廠家高傳輸效率,滿足同時傳輸幾種業(yè)務(wù)的需求,通常采用時分復用的方法,將若干個低速數(shù)字碼流按一定格式合并成一個高速數(shù)據(jù)碼流,以便在一條信道中傳輸,使各個業(yè)務(wù)信號互相不產(chǎn)生干擾,實現(xiàn)此功能的設(shè)備就是數(shù)字復接系統(tǒng)。

便攜式衛(wèi)星通信,要求實現(xiàn)平臺集成度高、速度快、功耗小、體積小和成本低。現(xiàn)場可編程門陣列(FPGA) 在結(jié)構(gòu)上由邏輯功能塊排列為陣列,并由可編程的內(nèi)部連線連接這些功能塊,共模電感來實現(xiàn)一定的邏輯功能。特別適合上述要求的產(chǎn)品開發(fā)與小批量生產(chǎn)。

FPGA 的開發(fā)環(huán)境在電路設(shè)計階段,可實時地對設(shè)計電路進行各種仿真分析,提高電路設(shè)計的靈活性和可靠性,特別是還可在成品上直接進行二次開發(fā)和功能擴展,靈活且可移植。后期還可以在線對任意一邏輯信號進行實時仿真,該文利用軟件Quartus II 5. 1 和VHDL 硬件語言進行設(shè)計和仿真,實現(xiàn)一個基于FPGA 的衛(wèi)星便攜站的同步數(shù)字復接系統(tǒng)的設(shè)計。

1 設(shè)計和實現(xiàn)

同步數(shù)字復分接器完成以下業(yè)務(wù)的復分接:3 路音頻合計48 kbps 數(shù)據(jù); 1 路64 kbps 同步數(shù)據(jù);1 路9. 6 kbps 異步數(shù)據(jù); 1 路128 kb共模電感器ps LAN 數(shù)據(jù); 1 路517. 2 kbps 視頻數(shù)據(jù)。采用同步、固定時隙分配和按位復接方式的設(shè)計方法。

1.1 準同步時延

因為數(shù)字復接器與音頻的接口關(guān)系最為復雜,所以設(shè)計要點著重放到了與音頻接口的處理。

1. 1. 1 音頻接口的乒乓操作

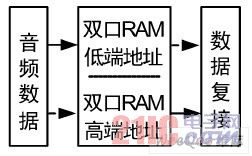

如圖1 所示,采用雙口RAM 完成音頻數(shù)據(jù)和復分接器的接口。音頻數(shù)據(jù)接口是一種DSP 總線接口,在第1 個緩沖周期,音頻數(shù)據(jù)緩存到雙口RAM的低端地址存儲區(qū),同時數(shù)據(jù)復接單元讀取雙口RAM 的高端地址存儲區(qū)的音頻數(shù)據(jù); 在第2 個緩沖周期,音頻數(shù)據(jù)緩存到雙口RAM 的高端地址存儲區(qū),同時數(shù)據(jù)復接單元讀取雙口RAM 的低端地址存儲區(qū)的音頻數(shù)據(jù)。如此循環(huán),周而復始。

圖1 乒乓操作示意圖

這樣經(jīng)過緩沖的數(shù)據(jù)流沒有時間停頓的送到復接器中,屬于一種流水線式處理,完成數(shù)據(jù)的無縫緩沖和處理,節(jié)約緩沖區(qū)的空間,達到利用低速模塊處理高速數(shù)據(jù)流的結(jié)果,實現(xiàn)了數(shù)據(jù)流的并串轉(zhuǎn)換。

如果音頻數(shù)據(jù)和復分接器的接口采用傳統(tǒng)的緩存方式,很容易造成復接器讀數(shù)據(jù)的時候音頻數(shù)據(jù)還沒有寫到緩存中,很容易造成聲音的“咔咔聲”,采用音頻接口的乒乓操作避免了此問題的產(chǎn)生。

1. 1. 2 提供唇音同步機制

在數(shù)字衛(wèi)星傳輸系統(tǒng)中,有一個獨特的音視頻同步問題,即通常說的唇音同步。由于圖像壓縮編碼所需之信號處理時間一般慢于聲音壓電感廠家縮編碼所需之信號處理時間,那么在收端將視頻及音頻信號解碼出來后,就會發(fā)現(xiàn)音頻比視頻快半拍。通常見到的情況是,或者口動時聽不到聲音,或者口不動時卻有聲音出來,即唇音不同步,給觀眾較差的主觀感覺。為了避免出現(xiàn)這一問題,分接器中提供了唇音同步單元,把音頻數(shù)據(jù)程序上進行延時,通過調(diào)整就可保證接收端的音和視頻同步。

1. 1. 3 解決FPGA 電路設(shè)計中的毛刺問題

在FPGA 中當多路信號同時發(fā)生跳變的瞬間,往往會出現(xiàn)一些不正確的尖峰信號,這些尖峰信號就是“毛刺”。組合邏輯電路中競爭冒險現(xiàn)象的出現(xiàn)也會出現(xiàn)“毛刺”。它的出現(xiàn)會影響電路工作的穩(wěn)定性和可靠性,導致數(shù)字系統(tǒng)的誤操作和邏輯紊亂。

設(shè)計中利用D 觸發(fā)器對輸入信號的毛刺不敏感的特點,去除信號中的毛刺,但是只是對信號中發(fā)生在非時鐘跳變沿的毛刺信號去除明顯,并且有一定延時色環(huán)電感器。因此設(shè)計中盡量采用同步時序電路來實現(xiàn)各個進程模塊的功能,同時對輸入輸出的數(shù)據(jù)進行高倍時鐘的采樣,達到去除電路中毛刺的目的。

1.2 設(shè)計方案

1.2.1 幀結(jié)構(gòu)

該單元不要求與其他復分接設(shè)備互聯(lián)互通,所以采用自定義的幀結(jié)構(gòu)。幀頭采用集中幀碼,幀頭固定為12 bits。幀結(jié)構(gòu)如表1 所示。

根據(jù)表1 可以計算出每幀的幀長L 為7 680 bit,線路速率R 為768 kbps 時,幀周期T 為:

大功率電感廠家 |大電流電感工廠