摘要:針對測控系統中設備分散,檢測環境惡劣的情況,設計了一種基于SOPC的以太網遠程數據采集系統。系統采樣基于NiosⅡ軟核的SOPC架構,以μC/OS-Ⅱ嵌入式實時操作系統為軟件運行平臺,以LWIP為以太網通信協議,實現了遠程數據采集和以太網傳輸及控制。整個系統在CycloneⅡEP2C35開發板上實現并通過驗證,實驗結果滿足設計要求并具有較好的應用前景。

關鍵詞:SOPC;以太網;NiosⅡ;LWIP;遠程數據采集

在工業測控系統中,往往存在現場檢測環境惡劣,設備分散,需要檢測系統具有遠程分布式數據采集功能,以實現設備的遠程檢測與監控。嵌入式以太網技術將以太網技術和嵌入式技術有機結合在一起,很好的滿足這種需求。Ethernet與傳統通訊接口相比,具有性價比高、傳輸距離遠、分布運行等特點;SOPC是基于FPGA解決方案的SOC,是MCU、DSP、FPGA的有機結合,具有體積小、功耗低、可靈活配置等優點。利用SOPC以太網技術將SOPC嵌入式測量模塊接入網絡進行控制,使其實現PC機所具有的遠近程測量控制和信息發布各項功能,讓工作人員遠離現場,仍可以對測量設備進行控制并獲得測量數據。

1 系統總體設計

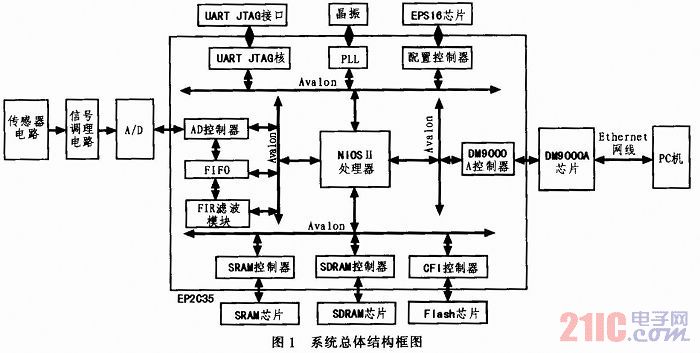

本系電感器設計統采用FPGA+NiosⅡ的架構進行設計。系統主要有數據采集模塊、FPGA模塊、存儲器模塊、網絡接口模塊組成,系統總體結構如圖1所示。首先將待測量經傳感器轉化為電信號,然后經前端信號調理,A/D轉換寫入FPGA片上FIFO,然后FPGA讀出數據經信號恢復、FIR數字濾波后存入RAM中,最后通過Ethernet傳輸到上位機進行顯示、診斷等處理。本方案可作為單獨采集系統和一臺計算機組成檢測系統;也可加入路由器,一個采集模塊與多臺計算機相連實現數據共享,或者一臺計算機與多個采集模塊相連,實現分布式檢測。

2 系統硬件設計

本設計采用的FPGA器件是Altera公司的一體電感Cyclone II系列EP2C35F672芯片。EP2C35內置35個18×18的硬件乘法器,有105個M4K RAM塊,共483 840位。在FPGA基礎上構建基于Nios II的SOPC系統,使用軟硬件協同的方法對A/D轉換器和網絡傳輸芯片進行控制。存儲器模塊包括SRAM、SDRAM、Flash 3種類型的存儲器。一片IDT71V416S256Kx16bits的SRAM,用作FPGA的緩存使用,存放運行的程序;一片A3V64S40ETP4 Mx16 bits的SDRAM,用來存儲程序運行的中間數據;一片AMD29LV128M123R 16 MB的FLASH存儲器,用來保存固化的程序和數據。為解決速率匹配、數據緩沖等問題,利用FPGA片上RAM資源設計8 k×16 bitsFIFO,將AD采樣的數據進行緩存。

2.1 數據采集模塊

數據采集模塊包括前端信號調理電路和A/D轉換電路。前端調理主要包括傳感器、調理電路。信號調理主要實現對模擬信號的緩沖、放大,以獲得ADC所滿足的輸入信號。

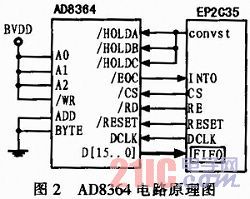

本設計采用的A/D轉化器為美國TI公司的ADS8364,ADS8364是高速、低功耗,六通道同步采樣16位并行輸出模數轉換器。采用+5 V工作電壓,當工作頻率為5 MHz時,其同步采樣為250 kHz,轉換時間4μs。六路模擬輸塑封電感入分為3組(A、B和C),每個輸入端都有一個保持信號來實現所有通道的同時采樣與轉換功能,適合于多路采集系統的需要。3個保持信號(/HOLDA,/HOLDB,/HOLDC)可以啟動指定通道的轉換,當3條HOLD線均為低電平時,6個模擬輸入同時被采樣。A0、A1、A2均接高,A/D轉換結果輸出FIFO模式。A/D轉換結束后產生轉換結束信號EOC,產生中斷。在轉換結束后,將數據讀入FPGA的FIFO中。AD8364與FPGA的連接如圖2所示。

2.2 網絡接口模塊

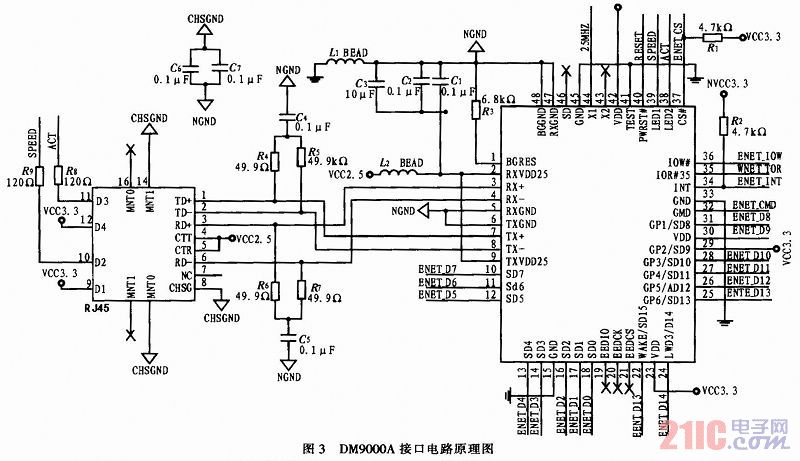

本設計的網絡芯片采用DAVICOM公司的DM9000A,該芯片具有通用處理器接口、一個10/100電感器生產廠家M PHY和4 kbytes的SRAM,是一款低功耗高性能的網絡控制器。DM9000A支持8位和16位兩種數據接口,本設計采用16位模式。其接口電路原理圖如圖3所示。

2.3 SOPC設計

FPGA硬件設計基于Altera公司的SOPC開發環境SOPC Builder.Altera公司為SOPC工具提供了眾多的IP核支持,可以直接調用。本設計中AD控制器需要自定制,用Verilog HDL編寫控制時序與接口邏輯,采用摩爾狀態機來產生ADS8364的轉換控制信號以及FIFO讀入時鐘。其控制模塊仿真波形如圖4所示。DM900A控制器使用友晶公司的DE2開發系統中為我們提供了DM900A控制器核。

大功率電感廠家 |大電流電感工廠