0 引 言

近年來,隨著DSP技術(shù)的普及、高性能DSP芯片的出現(xiàn),DSP已越來越多地被廣大的工程師所接受,并越來越廣泛地被應(yīng)用于各個領(lǐng)域,例如:語音處理、圖像處理、模式識別及工業(yè)控制等,并且已日益顯示出其巨大的優(yōu)越性。DSP是利用專門或通用的數(shù)字信號處理芯片,以數(shù)字計算的方法對信號進(jìn)行處理,具有處理速度快、靈活、精確、抗干擾能力強(qiáng)、體積小及可靠性高等優(yōu)點,滿足了對信號快速、精確、實時處理及控制的要求。

在語音處理、圖像處理、模式識別及工業(yè)控制中,少不了對必要的數(shù)據(jù)進(jìn)行存儲保護(hù)。如果存儲在內(nèi)外RAM之中,掉電數(shù)據(jù)就丟失,起不到保護(hù)數(shù)據(jù)電感器圖形符號的作用;存儲在FLASH中,由于對FLASH進(jìn)行數(shù)據(jù)寫入時,要先進(jìn)行擦除操作,然后才能整頁的寫入,如果每次寫入的數(shù)據(jù)比較少,這樣就要占據(jù)很大的CPU時間,操作比較麻煩。

針對這些缺點,根據(jù)多年的研發(fā)經(jīng)驗,結(jié)合實際,提出一種基于SP模壓電感I方式的外部數(shù)據(jù)擴(kuò)展方式。本文所用到的數(shù)據(jù)存儲器是Xicor公司生產(chǎn)的帶有塊鎖保護(hù)的4 Kb CMOS串行E2PROM X5043(接口符合SPI協(xié)議)。該器件利用Xicor專有的直接寫入晶片,提供最小為10萬次擦寫和最少100年的數(shù)據(jù)保存期。數(shù)據(jù)寫入之前不需要外部進(jìn)行擦除操作,芯片本身自動完成。同時X5043還具有上電復(fù)位、看門狗定時器、電源電壓監(jiān)控四種常用的功能。這種組合不但降低了系統(tǒng)成本、減少了電路板空間,還增加了系統(tǒng)可靠性。

1 SPI協(xié)議

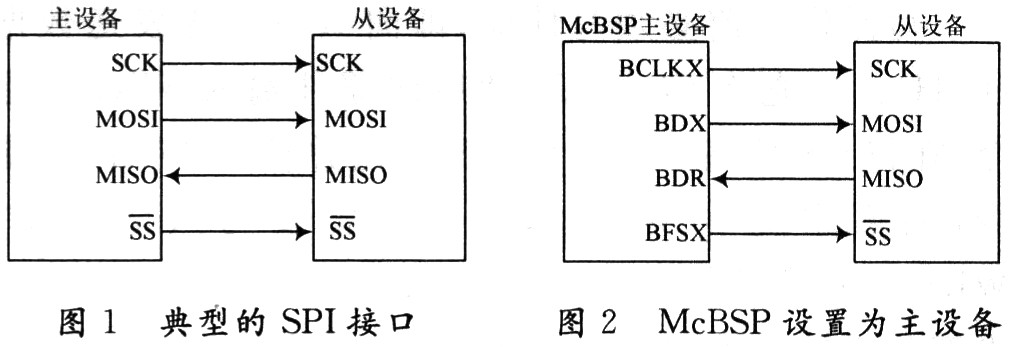

圖1是典型的SPI協(xié)議。SPI協(xié)議采用主從設(shè)置,相互連接的設(shè)備中一個作為主設(shè)備,其他的設(shè)備作為從設(shè)備。接口連線主要包括4條信號線:串行數(shù)據(jù)輸入信號線,(Master In Slave Out,MIS());串行數(shù)據(jù)輸出信號線(Master Out Slave In,MOSI);移位時鐘信號線(SCK);從設(shè)備片選信號線(SS)。

2 VC5402的多通道緩存串行口(McBSP)

2.1 McBSP的功能特點

TMS320V5402是TI生產(chǎn)的第二代低功耗定點數(shù)字信號處理器,提供了兩個高速、全雙工、多通道緩存串行口,每個串行口可以支持128通道,速度達(dá)100 Mb/s。McBSP是在標(biāo)準(zhǔn)串行接口的基礎(chǔ)之上對功能進(jìn)行擴(kuò)展,因此,具有與標(biāo)準(zhǔn)串行接口相同的基本功能:

模壓電感器 (1)全雙工通信;

(2)擁有兩級緩沖發(fā)送和三級緩沖接收數(shù)據(jù)寄存器,允許連續(xù)數(shù)據(jù)流傳輸;

(3)為數(shù)據(jù)發(fā)送和接收提供獨立的幀同步脈沖和時鐘信號;

(4)能夠與工業(yè)標(biāo)準(zhǔn)的解碼器、模擬接口芯片(AICs)和其他串行A/D和D/A設(shè)備直接連接;

(5)支持外部移位時鐘或內(nèi)部頻率可編程移位時鐘。

此外,McBSP還具有的其他特殊功能,本文所用到的有:

(1)串行字長度可選,包括8,12,16,20,24和32位可選。

(2)進(jìn)行8位數(shù)據(jù)傳輸時,可以選擇LSB或MSB為起始位;

(3)幀同步脈沖和時鐘信號的極性可編程;

(4)內(nèi)部時鐘和幀同步脈沖的產(chǎn)生可編程,具有相當(dāng)大的靈活性。

2.2 McBSP與X5043的接口設(shè)計

X5043的外部接口符號SPI協(xié)議規(guī)范。DIP封裝的X5一體電感器043有8個管腳組成,各個管腳功能如下所示:

CS:片選端,當(dāng)CS為低時,X5043選中。在任何操作之前,需要先在CS上有一次由高至低的跳變;

SO:串行數(shù)據(jù)輸出端,當(dāng)讀周期時,數(shù)據(jù)從該引腳移出;

SI:串行數(shù)據(jù)輸入引腳,所要寫入存儲器的操作碼,字節(jié)地址和數(shù)據(jù)都從該引腳輸入;

WP:當(dāng)WP為低時,向X5043的非易失性寫被禁止,但器件其他功能正常,為高時,所用功能電感生產(chǎn)廠家都正常;

SCK:串行時鐘端。串行時鐘控制串行總線數(shù)據(jù)輸入和輸出的時序。

McBSP的時鐘停止模式與SPI協(xié)議兼容。當(dāng)McBSP處于時鐘停止模式時,發(fā)送器和接收器是內(nèi)部同步的,因此可以將McBSP作為SPI主設(shè)備或從設(shè)備。當(dāng)設(shè)置McBSP為主設(shè)備時,發(fā)送端輸出信號DXR就作為SPI協(xié)議的MOSI信號,接收端輸入信號DRR就作為SPI協(xié)議的MISO信號。發(fā)送幀同步脈沖信號FSX作為從設(shè)備片選信號SS,而發(fā)送時鐘信號CLKX就與SPI協(xié)議的串行時鐘信號SCK相對應(yīng)。由于接收時鐘信號CLKR和接收幀同步脈沖信號FSR與發(fā)送端的相應(yīng)部分CLKX和FSX在內(nèi)部相互連接,因此這些信號不用于時鐘停止模式。該設(shè)計中McBSP作為主設(shè)備使用。X5043與McBSP的接口電路如圖2所示。