O 引言

脈沖壓縮體制在現(xiàn)代雷達(dá)中被廣泛采用,通過發(fā)射寬脈沖來提高發(fā)射的平均功率,保證足夠的作用距離;接收時則采用相應(yīng)的脈沖壓縮算法獲得脈寬較窄的脈沖,以提高距離分辨力,從而能夠很好地解決作用距離和距離分辨力之間的矛盾問題。

線性調(diào)頻(LFM)信號通過在寬脈沖內(nèi)附加載波線性調(diào)制以擴(kuò)展信號帶寬,從而獲得較大的壓縮比。所需匹配濾波器對回波信號的多普勒頻移不敏感,因此LMF信號在日前許多雷達(dá)系統(tǒng)中仍在廣泛使用。

本文基于快速傅里葉IP核可復(fù)用和重配置的特點,實現(xiàn)一種頻域的FPGA數(shù)字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設(shè)計靈活,調(diào)試方便,可擴(kuò)展性強(qiáng)的特點。

1 系統(tǒng)功能硬件實現(xiàn)方法

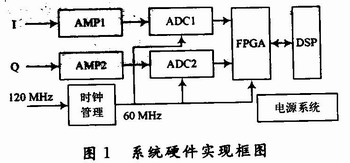

該系統(tǒng)為某寬帶雷達(dá)系統(tǒng)的數(shù)據(jù)采集和數(shù)字脈沖壓縮部分。系統(tǒng)要求在1個脈沖重復(fù)周期(PRT)內(nèi)完成距離通道的數(shù)據(jù)采集及1 024點的數(shù)字脈沖壓縮,并在當(dāng)前PRT將脈壓結(jié)果傳送至DSP,其硬件結(jié)構(gòu)如圖1所示。

數(shù)據(jù)采集系統(tǒng)主要包括前端的運算放大器和模/數(shù)轉(zhuǎn)換器。運算放大器選用ADI公司的AD8138,將輸入信號由單端轉(zhuǎn)換為差分形式以滿足ADC的輸入需 求,并且消除共模噪聲的影響。模/數(shù)轉(zhuǎn)換器選用TI公司的ADS5500,具有14 b的分辨率和125 MSPS的最高采樣率,用來對輸入LFM信號進(jìn)行60 MHz的高速采樣。

數(shù)字脈沖壓縮模塊在FPGA中實現(xiàn),F(xiàn)PGA選用Xilinx公司的XQ2V1000芯片。在對輸入采樣數(shù)據(jù)進(jìn)行脈沖壓縮后,結(jié)果存儲于FPGA片內(nèi)的雙口RAM中,并向DSP發(fā)送中斷信號。DSP在接收到中斷信號后讀取RAM中的脈壓數(shù)據(jù)進(jìn)行主處理。

2 脈沖壓縮模塊的設(shè)計和實現(xiàn)

2.1 脈沖壓縮原理

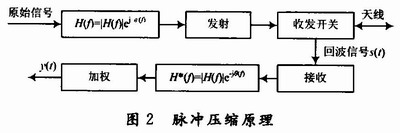

數(shù)字脈沖壓縮技術(shù)是匹配濾波和相關(guān)接收理論的實際應(yīng)用,頻域的匹配濾波等效于時域的相關(guān)接收。基于匹配濾波理論實現(xiàn)數(shù)字脈沖壓縮的原理如圖2所示。

圖2中θ(f)為發(fā)射信號的非線性相位譜,接收的回波信號在經(jīng)過匹配濾波后,非線性相位譜得到校正。輸出的窄脈沖為:

![]()

匹配濾波器有一個重要的特性:對波形相同而幅度和時延不同的信號具有適應(yīng)性。也就是說,與信號s(t)匹配的濾波器,對信號as(t-τ)也是匹配的。回波信號s(t)在波門中的位置反映在脈壓結(jié)果峰值出現(xiàn)的位置,這也是利用雷達(dá)脈沖進(jìn)行測距的主要依據(jù)。

2.2 脈沖壓縮原理

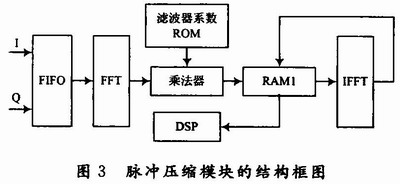

脈沖壓縮模塊包括FFT、與IFFT單元、復(fù)數(shù)乘法單元以及存儲單元,其結(jié)構(gòu)框圖如圖3所示。其中,F(xiàn)FT和IFFT單元是通過復(fù)用Xilinx公司提供的快速傅里葉變換IP核來實現(xiàn)的,而硬件乘法器則為復(fù)乘提供了解決途徑。

采樣數(shù)據(jù)首先存入FIFO中進(jìn)行全局緩存,然后FFT單元從FIFO中讀取采樣數(shù)據(jù),緊接著進(jìn)行FFT運算,結(jié)果在流水輸出時直接與匹配濾波器系數(shù)電感器廠家相乘, 并將運算結(jié)果寫入塊RAMl中,最后IFFT單元從塊RAMl中讀取復(fù)乘后的數(shù)據(jù)進(jìn)行IFFT(復(fù)用FFT運算IP核)運算,結(jié)果寫入塊RAMl后發(fā)送中 斷信號,等待DSP讀取。

2.2.1 FFT處理單元的硬件復(fù)用

在系統(tǒng)中FFT處理單元通過使用軟核Fast Fourier Transform v3.O來實現(xiàn)的。該IP核提供3種結(jié)構(gòu)選擇。

(1)管線級,數(shù)據(jù)流水I/0。這種結(jié)構(gòu)將若干基-2蝶形單元級聯(lián)起來,使得數(shù)據(jù)的輸入、計算、輸出可以流水進(jìn)行,從而可以達(dá)到很高的處理速度,但資源消耗較大;

(2)基-2,最少資源消耗。這種結(jié)構(gòu)采用單個基-2蝶形單元對輸入數(shù)據(jù)進(jìn)行變換,運算消耗的時間較長;

(3)基-4,突發(fā)I/O;這種結(jié)構(gòu)采用單個基-4蝶形單元對輸入數(shù)據(jù)進(jìn)行變換,并利用塊RAM來存儲旋轉(zhuǎn)因子,占用系統(tǒng)資源較少,在1個PRT內(nèi)可以完成脈壓結(jié)果的輸出,從而在資源和速度這兩者之間達(dá)到很好的平衡,也是設(shè)計中實際采用的結(jié)構(gòu)。 大功率電感廠家 |大電流電感工廠