摘要:本文針對傳統基準電壓的低PSR以及低輸出電壓的問題,通過采用LDO與帶隙基準的混合設計,并且采用BCD工藝,得到了一種可以輸出較高參考電壓的高PSR(電源抑制)帶隙基準。此帶隙基準的1.186 V輸出電壓在低頻時PSR為-145 dB,在0~1GHz頻帶內,最高PSR為-36 dB。在-50~150℃內,1.186 V基準的溫漂為7.5ppm/℃。

關鍵詞:電源抑制;級聯;帶隙基準;低壓差線性穩壓器;溫度系數

電子鎮流器的芯片內數字部分的干擾,這就給芯片的電源帶來較大的干擾。因此對芯片內基準的中頻PSR(Power Supply Rejection,電源抑制)有較大要求。本文從此角度在Brokaw帶隙基準的基礎上進行改進,采用LDO與基準的級聯設計來增加其PSR。

1 電路結構

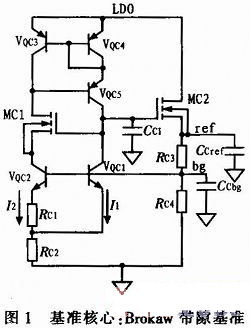

1.1 基準核心

目前的基準核心可以有多種實現方案:混合電阻,Buck voltage transfer cell,但是修調復雜,不宜工業化。本設計采用Br大電流電感okaw基準核心,其較易實現高壓基準輸出,并且其溫漂、PSR及啟動特性均較好。本文采用的改進的Brokaw基準核心的結構如圖1所示。

對此核心的分析:

三極管的輸出電流公式:

其中I是三極管射極電流,Is與射極面積成正比,n為一常數,取1。這里,取VQC2:VQC1=8:1,因此Is2=8xIs1,又I1=I2,分別代入(1)并相除,整理得:

其中Vbe1是負溫度系數,Vt是正溫度系數,RC2與RC1是同類電阻,溫度系數相抵消,選擇合理的RC2/RC1,就可以得到一階補償為0的基準電壓,可以很好的滿足本芯片的要求。

在電流鏡的選取上,采用威爾遜電流鏡,精度高,不需外加偏置電路,因此電源抑制比較高。輸出管采用mos管,對VQC5、VQC1支路電路影響小。通過增加MC1,使VQC2和VQC1的集電極電位相近,減小誤差。

產生的Vref為4.75 一體成型電感器V,在放大電壓的同時,PSR、溫漂均放大了4倍,即PSR升高了12 dB(在隨后的仿真波形中可以看到)。

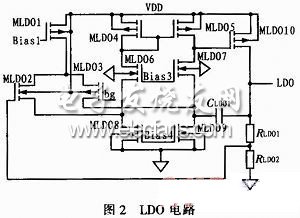

1.2 LD珠海電感廠O

LDO在低頻時的PSR主要取決于運放的增益,為此選擇折疊共源共柵電路。此LDO電路基于文獻中的電路修改,如圖2所示,并采用PSR高的偏置生成電路。

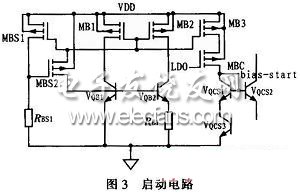

1. 3 啟動電路

Brokaw核心本身存在0狀態,VQC5基極為高電平,VQC2、VQC1基極為低電平,因此引入如圖3的啟動電路。

圖3中右下角即為啟動電路。對于常規Brokaw基準,當VQC2基極電壓低于啟動電壓時,VQCS2將VQC5基極電壓拉低VQC2基極電壓拉高,使電路啟動,所以VQCS2僅需很小的基極電流就可以使電路啟動。

但是,由于本設計采用LDO供電,而LDO的參考電壓是bg,存在死循環,即bg低,則LDO低,所以基準核心的VQC5無法給VQCS2提供電流,也就無法提高VQC2的電壓即bg,因此需要外界提供大電流bias-start,使得當LDO無法啟動基準核心時,此電流可以足夠大,在RC4上產生的壓降使bg達到足夠大,繼而LDO達到使基準核心啟動所需的最低電壓,從而使電路進入自動修正狀態,模壓電感最終使bg和ref達到指定電壓。

這樣雖然能啟動,但是,正常工作時,此大啟動電流bias-start將通過VQCS1和VQCS3流向地,增加了系統的負擔。因此,在電流輸出管MB3下加入控制管MBC,并使得在正常工作時,LDO的高電壓足以使MBC關斷,從而降低啟動電路的損耗。2 仿真與分析 大功率電感廠家 |大電流電感工廠