近年來,隨著集成芯片制造技術的發(fā)展,可編程邏輯器件(PLD)在速度和集成度兩方面得到了飛速提高。由于它具有功耗低、體積小、集成度高、速度快、開發(fā)周期短、費用低、用戶可定義功能及可重復編程和擦寫等許多優(yōu)點,應用領域不斷擴大,越來越多的電子系統(tǒng)開始采用可編程邏輯器件來實現(xiàn)數(shù)字信號處理,從而使通用DSP芯片難于完成的一些時序組合邏輯和某些簡單的大運算量的數(shù)學計算得以實現(xiàn)。繼QuickLogic和XILINX分別開發(fā)了內含嵌入式FIR core的CPLD之后,ALTERA公司又推出了新一代可編程邏輯器件Stratix系列,其性能完全滿足高速數(shù)字信號算是系統(tǒng)的設計要求。

1 Stratix系列器件的主要特性

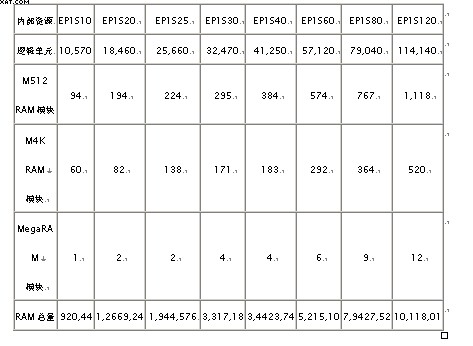

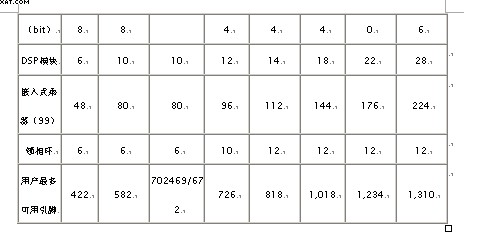

同其它含有嵌入式FIR core的CPLD相比較,Stratix系列CPLD采用了1.5V內核,0.13μm全銅工藝,由QuartusII 2.0以上版本軟件支持,可以重復編程,通過JTAG接口或者EPROM加載程序,內部有DSP模塊、PLL、大帶寬高速I/O接口和大容量存儲模塊。主要內部資源參見表1。

表1 Stratix器件內部資源表

|

|

•大容量存儲資源:Stratix器件中的TriMatrix存儲結構具有高達10Mbit的RAM和高達12Tbps的峰值存儲帶;有三種不的嵌入存儲模塊類型共模電感器,它們都具有混合寬度和混合時鐘模式嵌入移位寄存器功能,可用于多種不同的場合:

512bit M512模塊(512×1bit到32×18bit):512位模塊加上校驗,可用于接口速率適配的FIFO。

4Kbit M4K模塊(4096×1bit到128×36bit):4K位模塊加上校驗,可用于小型數(shù)據塊存儲和多通道I/O協(xié)議。

512Kbit MegaRAM模塊(64K×9bit到4K×144bit):512K位RAM加上校驗,可用于存儲大型數(shù)據塊或者Nios TM嵌入式處理器軟核代碼等。

其中,4Kbit M4K模塊和512Kbit MegaRAM模塊支持完全的雙端口模式。所有存儲資源分布在整個器件中,設計者可根據設計的存儲器類型和容量大小,通過Altera Quartus II軟件的MegaFunction函數(shù),靈活選擇電感器生產廠家不同參數(shù),配置成特定存儲容量的RAM、DPRAM、FIFO等特殊模塊。

•高帶寬DSP模塊:Stratix DSP模塊包括硬件乘法器、加法器、減法器、累加器和流水線寄存器。各個功能單元之間有專用的走線,具有針對Stratix器件內部大量存儲器的專用存儲器結構接口,因此通過優(yōu)化設計,DSP模塊可提供高達2.0GMACS的DSP性能,并且具有盡可能小的布線擁塞。

Altera Quartus II軟件的MegaFunction提供了多種DSP模塊操作模式。每一DSP模塊可針對不同的應用,通過選擇合適的DSP模塊操作模式,實現(xiàn)8個9×9位乘法器、4個18×18位乘法器或一個36×36位乘法器。當配置為36×36位乘法器模式時,DSP模式還可實現(xiàn)浮點算法。專用的乘法器電路支持帶符號和不帶符號乘法操作,并可在不帶來任何精度損失的情況下,動態(tài)地在兩種運算之間切換。

Stratix器件的DSP模塊提供了高于DSP處理器的數(shù)據處理能力,并工字電感且更為靈活和經濟。每一Stratix DSP模塊可提供多達8個運行在250MHz的并行乘法器,數(shù)據吞吐能力高達2GMACS。最大的Stratix器件EP1S125包括28個DSP模塊,可完成高達224個并行乘法操作,并提供56GMACS的總線數(shù)據吞吐能力;而傳統(tǒng)的DSP處理器最多smd功率電感器僅可同時進行8個并行乘法操作,數(shù)據吞吐量也只有8.8GMACS。除了DSP模塊中的專用乘法器以外,還可利用邏輯單元(LE)實現(xiàn)乘法器和DSP功能。例如,可在Stratix器件中利用大約9600個邏輯單元實現(xiàn)一個256階FIR濾波器。Stratix系列的EP1S120包括大約114140個邏輯單元,可以容納11個這樣的濾波器。每一濾波器可運行在200MHz,這意味著通過利用LE可提供563GMACS的器件總吞吐能力。結合DSP模塊提供的56GMACS數(shù)據吞吐能力,Stratix器件可提供高達620GMACS的數(shù)據總吞吐能力。因此Stratix器件適用于大數(shù)據量數(shù)字信號處理。

大功率電感廠家 |大電流電感工廠