摘要:低功耗是嵌入式系統的發展趨勢,也是便攜式嵌入式設備設計中要解決的關鍵問題之一。對影響嵌入式系統功耗的因素進行了分析,指出了降低系統功耗的途徑,從硬件設計和軟件設計兩個方面闡述了超低功耗嵌入式系統設計的技巧。

關鍵詞:超低功耗;嵌入式系統;硬件設計;軟件設計

無論是在軍事還是在商業上的應用,便攜式插件電感嵌入式系統一般是由可充電電池來供電的,因此,采用有效的節能技巧來改進系統的軟硬件設計,降低系統的功耗以增加電池供電設備的使用時間,是便攜式嵌入式系統設計中需要研究和解決的關鍵問題。

1 影響功耗的因素

1.1 集成電路功耗

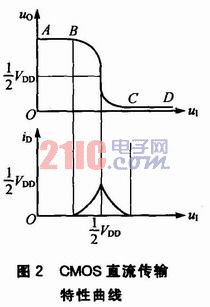

CMOS倒相器在集成電路分析中具有非常重要的意義,常用它來進行集成電路延遲時間和功耗的分析。CMOS倒相器如圖1所示,圖2是倒相器的直流傳輸特性曲線。

若電路處在靜態(不發生狀態翻轉)并忽略漏電流的前提下,反相器的功耗幾乎為零,如圖2中的AB段和CD段。當電路發生狀態翻轉時,N管和P管具有同時導通的一段時間,此時從電源通過2個管子流向地的電流iD達到一個很高的峰值,如圖2對應于BC段的電流。很大的電流意味著較高的功率消耗和熱能的損失,這在時鐘頻率較高時尤為突出。時鐘速度越高意味著每秒鐘狀態的切換次數就越多,也意味著更多的電能損耗。除此之外,在工作時還存在著靜態漏電功耗,下面對這2類功耗分別進行分析。

1.1.1 動態功耗

CMOS倒相器從一種穩定工作狀態突然轉變到另一種穩定狀態的過程中,將產生附加的功耗,稱之為動態功耗。這一功耗是由2部分組成的,一部分是瞬時導通功耗PT,另一部分是對負載電容充放電所消耗插件電感器的功率PC,其表達式為:

![]()

式(1)中,VDD為電源電壓;ITC為2個管同時導通所產生的瞬時電流,不是固定的數值,如圖2所示;a為活動因子,表示電容充放電的平均次數相對于開關頻率的比值;CL為進行充放電的等效負載電容,包括柵繞行電感器電容、節點電容、互連電容等;f為開關頻率,即電路的工作頻率。

1.1.2 靜態漏電功耗

靜態漏電功耗是由亞閾值電流和反向偏壓電流造成的。在集成電路中,動態功耗是整個CMOS集成電路功耗的主要組成部分,一般約占電路總功耗的90%以上,靜態漏電功耗占電路總功耗的1%以下,因而在大多數情況下可以忽略。

1.2 其他功耗

①純電阻元件上消耗的功率。電阻為耗能元件,只要電路中使用電阻,就存在著能量消耗。

②有源開關器件在狀態轉換時,電流和電壓比較大,將引起功率消耗。

③非理想元件由于等效電阻的存在而消耗的功率。如電路中的儲能元件電感和電容,理想情況下它們是不消耗能量的,但是實際使用的電感和電容都存在著等效串聯電阻(ESR),就意味著能量的消耗。

④印制電路板中的走線上消耗的功率,如電源線由于電阻的存在會造成電能的損耗,實際中地線上也存在著電流的流動。電感器課件由于導線阻抗的存在,串聯單點接地的不同接地點之間會存在著電位差,因此在這些地線上也存在著能量的消耗。

2 降低系統功耗的途徑

①降低集成電路的動態功耗。根據式(1)可知,要降低集成電路的動態功耗,途徑有:a.降低活動因子,也就是降低電容充放電的平均次數。b.降低電源電壓。因為動態功耗與電壓的平方成正比,瞬時導通功耗與電壓成正比,因此在滿足電路速度的前提之下,降低電源電壓是降低電路功耗的最有效的辦法。c.降低負載電容。為了減小負載電感器廠家電容,在工藝方面可以選擇小的器件,物理實現時減小連線的長度。d.降低開關頻率,在式(1)中,電路的功耗與工作頻率成正比,因此降低時鐘頻率可以直接降低動態功耗。

②盡可能選用靜態功耗小的CMOS集成芯片,以降低系統的靜態漏電功耗。

③盡可能地減少純電阻的使用。純電阻是耗能元件,電能直接轉化為熱能消耗掉了,所以要盡可能地避免電阻的使用。 大功率電感廠家 |大電流電感工廠