為了方便對1553B設備進行測試,介紹了一種基于ARM9平臺和FPGA的1553B總線測試系統的設計與實現方法。該系統以LPC3250作為微處理器,以CYCLONE I系列的EP1C6Q240C8芯片實現ARM與1553B協議芯片的接口邏輯。在Linux操作系統2.6內核下實現1553B的驅動程序。15 53B協議芯片采用BU-64843T8,以實現系統的便攜性。

隨著航空電子系統的發展,多路數據傳輸數據總線在航空電子系統中起著越來越重要的作用,其主要特點是集中控制、實時性要求高、分布處理。1553B 總線以其具有較高的可靠性和靈活性,廣泛應用于軍事、航空航天系統。傳統的1553B測試設備采用普通計算機或工控機作為測試平臺,通過PCI總線與被測設備通信,這對測試設備的攜帶造成極大不便。本文所闡述的測試系統以ARM9作為中央處理器,以DDC的BU-64843T7作為1553B協議芯片,從而實現系統的小型化和便攜化,應用FPGA實現ARM時序與1553B時序的轉換,并采用Linux操作系統以確保系統穩定可靠。

1 ARM與FPGA數據通信接口設計

1. 1 系統硬件介紹

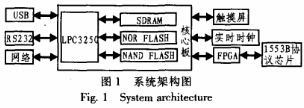

該系統硬件由LPC3250核心板、外擴接口電路、FPGA和1553B協議芯片組成組成。系統架構如圖1所示。

LPC3250微處理器面向低功耗、高性能的應用,采用ARM926EJ-S CPU內核,實現5級流水處理并采用哈佛結構,可工作在266 MHz的頻率下,數據處理能力強大。

本系統外擴USB、RS232和網絡接口,用于操作系統的燒寫和驅動程序、應用程序的調試,并且配備實時時鐘,可以掉電保持。為增加其可靠性,本系統在多處增加ESD芯片,以增強系統的抗靜電能力。 大功率電感廠家 |大電流電感工廠