隨著工藝技術向65nm以及更小尺寸的邁進,出現了兩類關鍵的開發問題:待機功耗和開發成本。這兩個問題在每一新的工藝節點上都非常突出,現在已經成為設計團隊面臨的主要問題。在設計方法上從專用集成電路功率電感(ASIC)和專用標準產品(ASSP)轉向可編程邏輯器件(PLD)將有助于解決這些問題。

過去,半導體行業一直關注的兩個目標是縮小體積和提高速率。近40年來,對這些目標的追求促使行業發展符合摩爾定律,性能和電路密度每18個月翻倍。導致技術高速發展,蘊育了計算機革命、互聯網革命以及現在的無線通信革命。

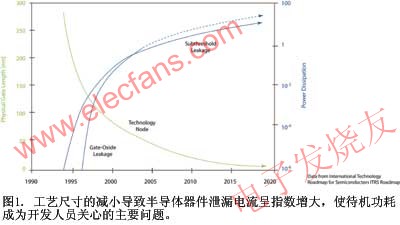

但同時也為此付出了代價。一種代價是物理上的。工藝技術上的每一次進步都使得芯片晶體管的“關斷”電扁平線圈電感流增加,也就是待機功耗在增加。另一代價是金錢。每一工藝節點的開發成本呈指數增加。65nm時代的設計必須解決這些代價問題。

人們采用了很多系統級和芯片級方法來處理動態功耗。在系統級上,采用動態功耗管理技術,確保只對工作電路上電,大大降低了器件的平均功耗,從而減少了和功耗相關的問題。

工藝上的進步降低了芯片級的動態功耗

一是縮小了晶體管體積,減小了晶體管的等效電容(C)。因此,縮小體積使動態功耗隨之線性下降。同樣,減小供電電壓會使動態功耗呈指數下降,是降低動態功耗的重要措施。0.9V~1.0V范圍內的供電方式幾乎都采取了這一措施來降低功耗。

降低動態功耗的另一工藝進步是在130nm工藝上引入了全銅互聯和低K金屬層絕緣技術。這些工藝創新大大降低了互聯阻抗和電容,不但減小了晶體管開關功耗,而且還降低了芯片信號和內部電源走線的IR壓降。

動態功耗下降而漏電流增大

然而,半導體物理規律卻表明工藝尺寸下降對待機功耗有不利的影響。工藝尺寸縮小后,隨著晶體管邏輯門厚度和溝道長度的減小,這些晶體管的柵極和漏極泄漏電流呈指數增大(圖1),而這是影響待機功耗的主要因素。通過使用較長的溝道以及較厚的氧化層來控制泄漏電流將導致開關速率下降,因此,工藝開發人員不得不折衷考慮速率和功耗。

工藝尺寸縮小,連線的寬度和高度也隨之減小,對功耗有不利的影響。減小銅連線的尺寸增強了電子散射和粒子邊界效應。從而增大了連線阻抗,導致一體成型電感器電路延遲和IR壓降增大。在45nm以下,這些效應會更加明顯。

工藝尺寸不斷縮小的結果之一是導致待機功耗成為芯片總功耗中的重要因素。同時,芯片用戶關心的問題從動態功耗轉向待機功耗。由于待機功耗的增大,許多通信器件分開考慮總功耗預算和待機功耗預算,并逐步增加待機功耗預算的比例。由于這些器件大部分時間處于待機模式,因此,待機功耗成為最主要的問題。

與動態功耗不同,還沒有簡單的方法來降低待機功耗。芯片開發人員不得不使用復雜的工藝和電路設計方法,犧牲晶體管速率來提高Vt,并采取延長溝道長度等措施。

目前已經有技術突破來解決速率和待機功耗的問題。一種是應變硅,該技術將空穴和電子對的移動能力提高了50%,從而提升了器件速率。與其它技術進步不同,應變硅雖然提高了速率,但是并沒有增加待機功耗。然而,它必須在芯片設計中采用新的布版規則,要求較嚴,導致了限制設計規則(RDR)這一概念的產生。RDR和可制造設計(DFM)在65nm以及更小工藝尺寸上越來越重要。

設計規則使開發過程越來越復雜

DFM重要性的增加以及RD一體成型電感器R的出現導致芯片設計更加復插件電感雜。物理設計尤其需要更多的資源和簡捷的物理設計自動工具。這些規則妨礙了版層重用,增加了新技術采用硬件IP模塊的難度。結果導致在芯片設計上加大投入,需要更多的資源來處理新技術中的布版和設計問題。

除了越來越高的開發成本以外,芯片開發人員還面臨其它的成本難題。65nm器件僅模板成本就高達2百萬美元,而45nm器件模板成本會超過3百萬美元。理想情況下,強大的財務支持是任何業務投入的基礎,包括芯片開發計劃等。然而,很多芯片開發項目缺乏足夠的資金支持。 大功率電感廠家 |大電流電感工廠